회로도 검증 끝나고 PCB 레이아웃 시작했다. 부품 배치하고 선 연결하면 끝인 줄 알았는데, 여기서 또 몇 주를 날렸다.

고전압 이격거리

72V 시스템이다. IPC-2221 찾아보니까 고전압 패턴 간 이격거리가 나온다.

내부 레이어 기준으로 계산하면 72V면 거의 20mm 가까이 띄워야 한다? 말이 안 됐다. 그렇게 하면 PCB가 A4 용지만 해진다.

선배한테 물어보니까 “그건 Bare PCB 기준이고, 코팅하면 줄어든다. 72V면 1mm 정도면 된다"고 하셨다.

반신반의하면서 1mm로 설계했다. 제작 후 내압 테스트 돌렸더니 500V에서 아크가 튀었다.

확인해보니까 솔더 마스크가 벗겨진 부분이 있었다. 제조 과정에서 생긴 핀홀인데, 거기로 아크가 튀었다. 0.3mm도 안 되는 구멍 하나 때문에.

결국 1.5mm 이상으로 재설계했다. 이론적 이격거리에 제조 마진까지 더해야 한다는 걸 배웠다.

Kelvin 연결

이거 몰라서 2주 날렸다.

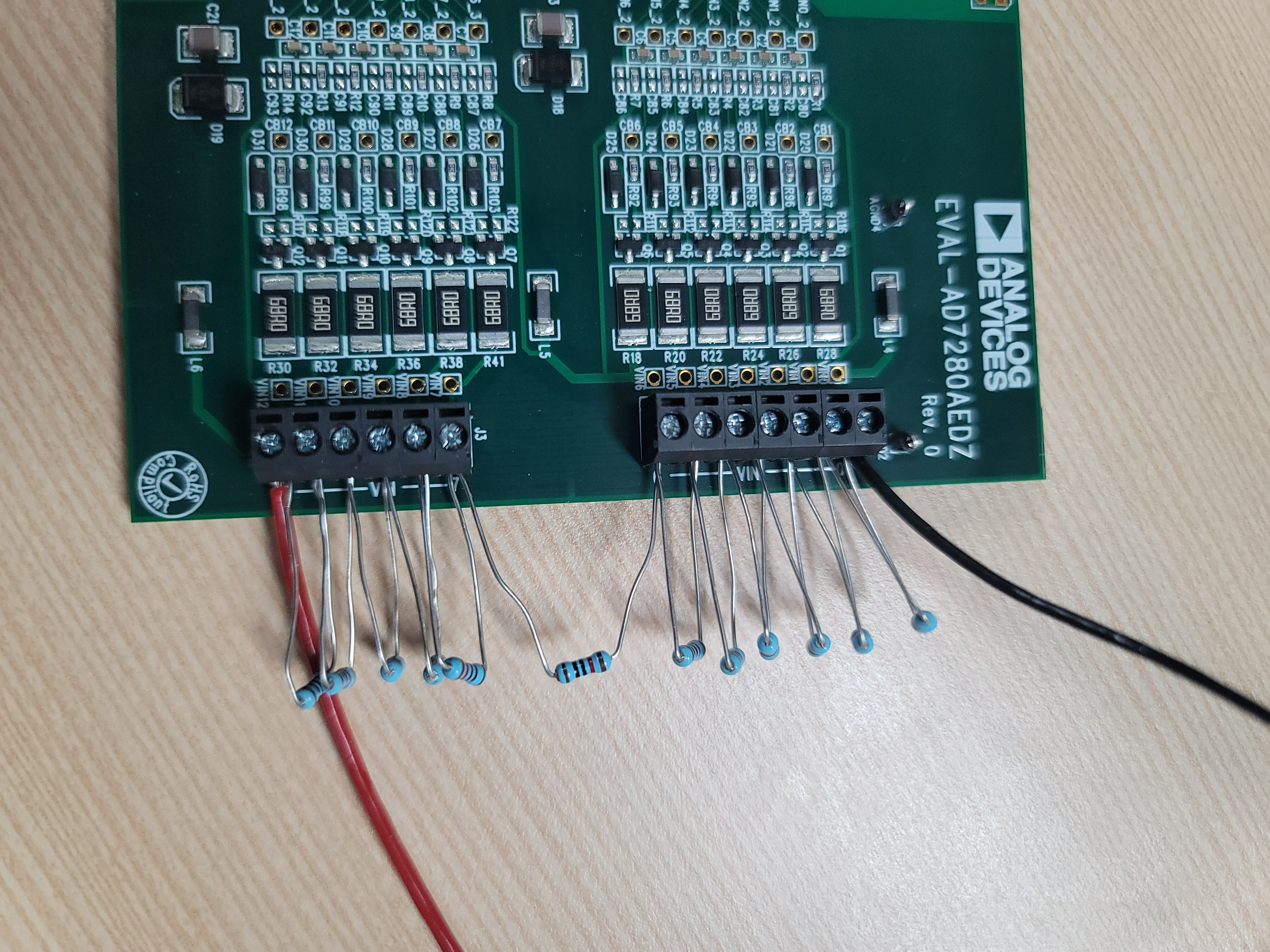

전류 센싱용으로 10mΩ 션트 저항을 달았다. 양단 전압을 ADC로 읽으면 되는 간단한 구조다.

100A 흘리면 1mV가 나와야 하는데, 1.3mV가 나왔다. 30% 오차.

처음엔 ADC 문제인 줄 알았다. 캘리브레이션도 해보고 별짓 다 했는데 안 됐다.

결국 검색하다가 Kelvin 연결(4선식 측정)이라는 걸 알게 됐다. 센스 라인을 전류 경로에서 분기하면 배선 저항까지 측정에 포함된다. 션트 저항 패드에서 직접 센스 라인을 빼야 한다.

잘못된 방식:

전류 경로 ──┬── 션트 ──┬──

│ │

센스+ 센스- ← 배선 저항 포함됨

올바른 방식 (Kelvin):

전류 경로 ──── 션트 ────

↑ ↑

센스+ 센스- ← 션트 패드에서 직접 분기

PCB 재설계해서 션트 저항에 별도 센스 패드 추가했더니 오차가 2% 이내로 줄었다.

열 관리

밸런싱 저항 24개가 각각 0.3W씩 발열한다. 총 7W 정도.

처음엔 공간 아낀다고 다닥다닥 붙여놨다.

테스트 5분 만에 PCB 표면 온도가 80도 넘게 올라갔다. 손도 못 대겠더라.

열화상 카메라로 찍어보니까 가운데 저항들이 빨갛게 타오르고 있었다. 열이 빠져나갈 데가 없었다.

체커보드 패턴으로 분산 배치하고, 저항 아래 써멀 비아 추가하고, 뒷면에 GND 구리박으로 방열판 역할 하게 했더니 65도 정도로 떨어졌다.

아날로그/디지털 분리

AD7280A는 아날로그 IC다. STM32는 72MHz 디지털.

둘을 같은 PCB에 넣으니까 ADC 값에 노이즈가 튀었다. MCU 클럭 타이밍에 정확히 맞춰서 스파이크가 생겼다.

AGND랑 DGND를 분리 안 했다.

4층 PCB로 바꾸고, 아날로그/디지털 영역을 물리적으로 나눴다. 두 GND는 한 점에서만 연결. 노이즈가 ±3mV로 줄었다.

데이지체인 신호선

4개 디바이스 연결하는 SPI 라인. 1MHz라서 느린 편이니까 대충 연결해도 될 줄 알았다.

Dev 0, 1은 잘 되는데 Dev 3 통신이 간헐적으로 실패했다.

파형 보니까 신호가 찌그러져 있었다. 20cm 배선이 안테나처럼 동작해서 링잉이 생겼다.

모든 디바이스를 일렬로 배치하고, 배선 길이를 최대한 줄이고, 시리즈 저항 33Ω 추가했더니 안정됐다.

테스트 포인트

첫 번째 PCB에는 테스트 포인트가 하나도 없었다. 공간 낭비라고 생각했다.

문제 생기니까 측정할 데가 없었다. 매번 0.5mm 피치 IC 핀에 프로브를 갖다 대야 했다.

한 번은 프로브가 미끄러지면서 두 핀을 쇼트시켰다. IC 죽었다. 5만원.

그 뒤로 모든 중요 신호에 테스트 포인트를 넣었다. VDD, SPI 라인, Alert, 셀 전압 몇 개, 션트 양단, GND 등등.

정리

PCB 레이아웃에서 배운 것들:

- 고전압 이격은 이론값 + 제조 마진

- 전류 측정은 Kelvin 연결

- 발열 부품은 분산 배치 + 써멀 비아

- AGND/DGND 분리

- 고속(?) 신호도 배선 길이 신경 써야 함

- 테스트 포인트는 돈 아끼려다 더 큰 돈 나감

회로도가 맞아도 레이아웃이 틀리면 동작 안 한다.

다음은 부품 선정 얘기. “아무 저항이나 1kΩ” 했다가 생긴 일.