지난 글 요약

지난 글에서 48V를 직접 넣으면 IC가 터진다는 걸 알았다. 이번에는 실제로 EVAL 보드에 전원을 어떻게 연결해야 하는지 삽질한 이야기다.

배터리 시뮬레이터가 있을 줄 알았다

비싼 평가보드니까 당연히 테스트용 저항 분배기가 내장되어 있을 거라고 생각했다. 파워서플라이 하나만 연결하면 알아서 셀 전압이 분배될 줄 알았는데…

UG-252 매뉴얼을 열어보니 그런 거 없었다.

실제 회로 구성

J2 (7핀) ──→ R1~R7 (10kΩ 직렬 보호저항) ──→ VIN0~VIN6 (U1)

J3 (6핀) ──→ R8~R14 (10kΩ 직렬 보호저항) ──→ VIN7~VIN12 (U2)

R1R14는 입력 보호용 직렬 저항이지, 전압 분배용이 아니다. 100nF 필터 커패시터(C1C12)도 있지만 역시 분배 기능은 없다.

결국 외부에서 셀 전압을 만들어서 넣어줘야 한다.

커넥터 핀 배치 이해하기

이게 처음에 좀 헷갈렸다.

J2 커넥터 (하위 6셀, U1)

| 핀 | 신호 | 설명 |

|---|---|---|

| J2-1 | VIN0 | Cell 1 하단 (VSS, GND) |

| J2-2 | VIN1 | Cell 1 상단 / Cell 2 하단 |

| J2-3 | VIN2 | Cell 2 상단 / Cell 3 하단 |

| J2-4 | VIN3 | Cell 3 상단 / Cell 4 하단 |

| J2-5 | VIN4 | Cell 4 상단 / Cell 5 하단 |

| J2-6 | VIN5 | Cell 5 상단 / Cell 6 하단 |

| J2-7 | VIN6 | Cell 6 상단 (VDD) |

J3 커넥터 (상위 6셀, U2)

| 핀 | 신호 | 설명 |

|---|---|---|

| J3-1 | VIN7 | Cell 7 하단 (= J2-7과 연결) |

| J3-2 | VIN8 | Cell 7 상단 / Cell 8 하단 |

| J3-3 | VIN9 | Cell 8 상단 / Cell 9 하단 |

| J3-4 | VIN10 | Cell 9 상단 / Cell 10 하단 |

| J3-5 | VIN11 | Cell 10 상단 / Cell 11 하단 |

| J3-6 | VIN12 | Cell 11 상단 / Cell 12 상단 (VDD) |

중요: J2-7과 J3-1은 내부에서 연결되어 있다. 상위/하위 IC의 경계점이다.

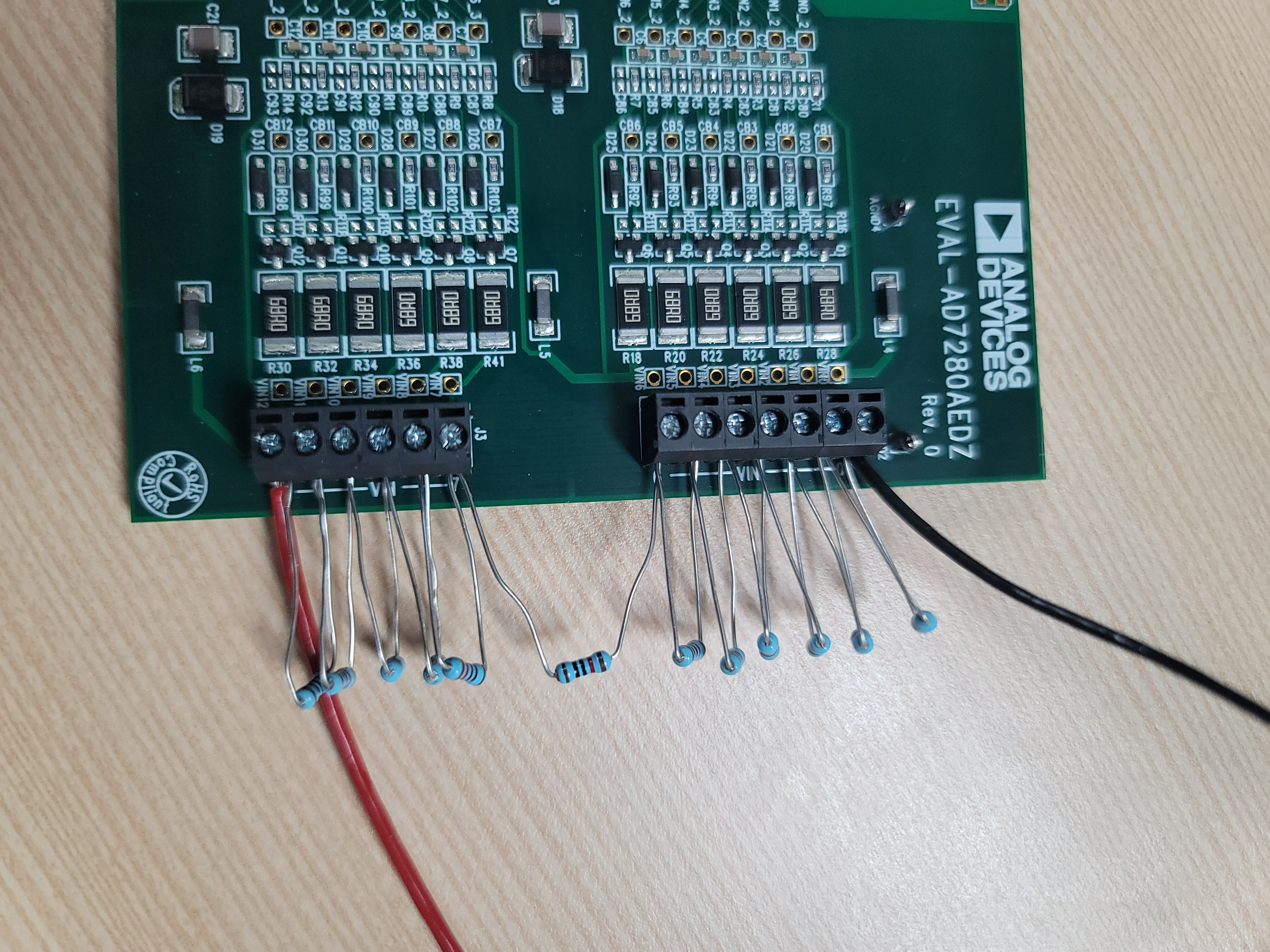

테스트 환경 구성: 터미널 블록에 저항 직접 연결

빵판 쓰려다가 접촉 불량이 걱정돼서, 터미널 블록에 저항을 직접 꽂는 방식을 선택했다.

연결 방법

J2, J3 터미널 블록의 인접한 핀 사이에 저항 리드선을 직접 꽂아서 데이지체인처럼 연결한다.

48V (+) ──┬── J3-6 (VIN12)

4kΩ (저항 리드선 직접 연결)

├── J3-5 (VIN11)

4kΩ

├── J3-4 (VIN10)

... (반복)

├── J3-1 / J2-7 (경계점)

4kΩ

├── J2-6 (VIN5)

... (반복)

4kΩ

GND (-)───┴── J2-1 (VIN0)

사용한 부품

- 저항: 4kΩ 금속피막 저항 (1% 정밀도, 파란 띠)

- 전원: 48V 파워서플라이 (빨간선 +, 검은선 -)

이 방식의 장점

- 접촉 불량 최소화 - 터미널 블록 나사로 확실하게 고정

- 별도 지그 불필요 - 저항만 있으면 됨

- 직관적 - 회로도 그대로 물리적으로 구현

저항 선정 시 고려사항

- 저항값: 1kΩ ~ 10kΩ 범위. 너무 작으면 발열, 너무 크면 노이즈 영향

- 정격 전력: 48V / 12 = 4V, 4V² / 4kΩ = 4mW. 1/4W면 충분

- 정밀도: 1% 금속피막 권장. 셀 편차 테스트하려면 정밀해야 함

삽질 포인트

- 평가보드에 배터리 시뮬레이터 없음 - 직접 만들어야 함

- J2-7과 J3-1 연결 관계 - 데이지체인 경계점, 여기서 헷갈리면 안 됨

- 터미널 블록 나사 조임 - 헐거우면 접촉 저항 생겨서 측정값 튐

다음 글에서는 드디어 SPI 통신을 시도한다. 여기서도 삽질이 기다리고 있었다.